Helioボード同梱のLED制御Webアプリを動かす

はじめに

前回は、HelioボードでLinuxをブートできるようにしました。 今回は、Helio SDイメージに同梱されている、LED制御Webアプリを動作させます。LED制御デモを動作させるのにGolden Hardware Reference Design (GHRD)が必要になるのですが、その理由を明らかにします。 Qsysを用いてGHRDでARMプロセッサとオンボードのLEDがどのようにインターコネクトされているのかも確認します。

Golden Hardware Reference Design (GHRD)の入手

Helio Resources for Rev.1.4にあるhelio_ghrd_5csxc5_v14.0.zipをダウンロードし、展開します。

FPGAへのGHRDの書き込み

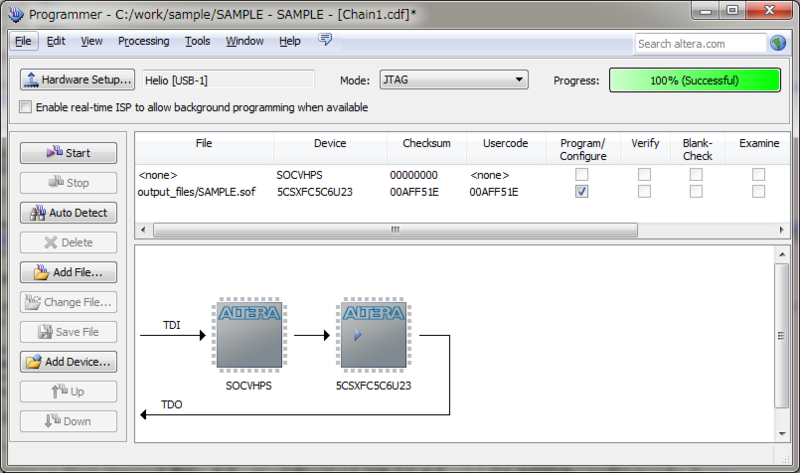

GHRDのoutput_filesディレクトリにはhelio_ghrd_top.sofがすでにあります。 ですので、ビルド工程をスキップしてFPGAにhelio_ghrd_top.sofを書き込みできます。 今回は同梱のSOFファイルを用いてFPGAに書き込んでみます。(時間短縮の意味でも楽です)

HelioをONにしてオンボードUSB Blaster IIにUSBケーブルを接続した状態で以下の手順を実施します。

- Quartus IIを起動します。

- File -> Open Projectを選択します。

- 展開したzipファイルのトップディレクトリにある「helio_ghrd_top.qpf」を選択します。

- Tools -> Programmerを選択します。

- Hardware SetupでHelioを選択します。

- Auto Detectを選択します。 7.「5CSXFC5C6」を選択します。

- 「5CSXFC5C6」を選択し、Deleteキーを入力します。SOCVHPSだけが残った状態にします。

- Add Fileを選択します。helio_ghrd_5csxc5_v14.0/output_files/helio_ghrd_top.sofを選択します。

- Startを選択します。

- 正常に書き込まれたら、Progressが100%になります。

成功すると、LEDがウエーブのように点灯します。

Linuxの起動

Helioの電源を入れた状態で以下の手順を実施します。

- USBケーブルをUARTに接続しなおします。

- LANケーブルを接続します。

- Tera Termでシリアル接続します。

- Warm Resetボタン(SW6)を押します。HPSにリセットがかかってLinuxが起動します。

LED制御デモ

ブラウザからHelioのIPアドレスにアクセスします。 アクセスしたページにLED制御デモがあるので試してみます。 LEDのウエーブの速さを変更したり、特定のLEDを点灯/消灯したりできます。

Webアプリと言ってもシンプルで、シェルスクリプトベースのCGIで組まれていて、LED制御プログラムをCGIから叩く仕組みになっているようです。

root@socfpga:/www/pages/cgi-bin# ls blink index.sh scroll_client scroll_server toggle

ちなみに、このディレクトリにある「blink」バイナリに対してstringsをかけてみると、「/sys/class/leds/fpga_led%d/」のような文字列が見つかります。 これから推測すると、おそらく、LEDを制御するデバイスドライバが別にあって、Sysfs経由でLED制御できるようにしてあるのだと思います。

root@socfpga:/www/pages/cgi-bin# strings blink

/lib/ld-linux-armhf.so.3

libpthread.so.0

_Jv_RegisterClasses

__gmon_start__

libc.so.6

sprintf

fopen

abort

fgets

fputs

fclose

fwrite

atoi

strcmp

__libc_start_main

GLIBC_2.4

xg{o

x`9`

x`9`H

?0F9FBF

/sys/class/leds/fpga_led%d/trigger

Failed to open the file %s

/sys/class/leds/fpga_led%d/brightness

none

--help

Usage %s: <LED number> <Blink delay (in ms)>

Invalid LED number. Valid LED range is 0-3

Invalid blink delay.

/home/root/.altera/frequency_fifo_scroll

Failed opening fifo frequency_fifo_scroll

/home/root/.altera/get_scroll_fifo

Failed opening fifo get_scroll_fifo

LED is scrolling.

Disable scroll_client before changing blink delay

/sys/class/leds/fpga_led%d/delay_on

/sys/class/leds/fpga_led%d/delay_off

timer

なぜGolden Hardware Reference Design (GHRD)が必要なのか?

GHRDにはHelioボードのHPS、LEDやボタンなどのサブシステム間のインターコネクトに関する情報などが入っていて、これをFPGAに書き込むことで、配線情報に従って結線されます。 つまり、LED制御デモが動かなかった原因は、GHRDをFPGAに書き込まないと、何も結線されていないので、ARMプロセッサからLEDが見えないため、ということになります。

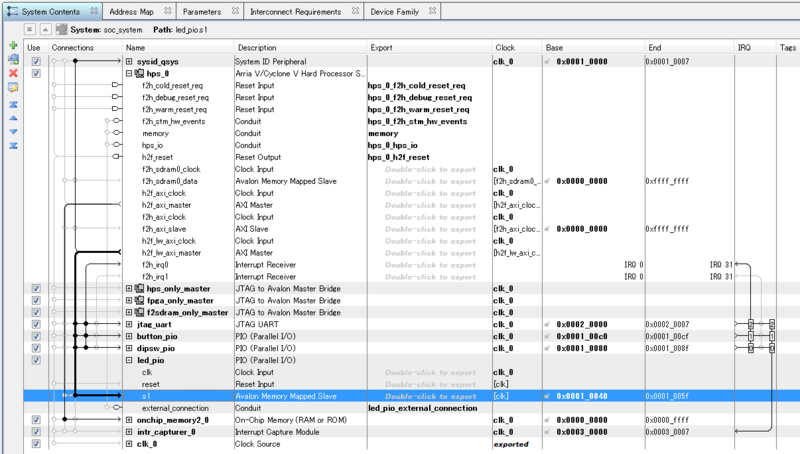

Qsysによるインターコネクトの確認

GHRDのインターコネクトはQsysで確認できます。

- Qsysを起動します。

- helio_ghrd_5csxc5_v14.0/soc_system.qsysを選択します。

hps_0は、ARMプロセッサのインタフェースです。 led_pioは、LED制御用のパラレルインタフェースです。 hps_0のh2f_lw_axi_master(※)とled_pioのs1が結線されていることがわかります。これは、つまり、ARMプロセッサからMemory-mapped I/Oでパラレル接続されているLEDを制御する、ということを意味しています。

※h2fとはHPS to FPGAのことで、信号の方向を表現しています。

led_pioはPIOコアと呼ばれるIPコアを用いています。詳細仕様は、led_pioをダブルクリックして、Detailsボタンを選択するとデータシートへのリンクがあるので、そちらを参照します。

led_pioのパラメータを確認すると、Widthが4になっているので、4bitのパラレルインタフェースであることがわかります。制御対象のオンボードLEDの個数と一致しています。

おわりに

LEDをCGIから制御するデモが動きました。 QsysでGolden Hardware Reference Desigのインターコネクトを確認することで、Helioボード同梱のLED制御デモでは、ARMプロセッサからMemory-mapped I/OでLEDを制御していることがわかりました。今回の経験から、ARMプロセッサとFPGAの世界をつなぐ手法としてMemory-mapped I/Oの理解がポイントになりそうです。

HelioボードでLinuxをブートする

はじめに

Helioボードは、FPGAとARMプロセッサが同居しており、Linuxをブートできます。 今回はHelioボードでLinuxをブートできるようにします。 HelioボードにLAN接続することで、同梱のWebサーバやsshdにPCからアクセスできるようになります。

準備

以下を事前に用意しておきます。

- SDカードリーダー

- LANケーブル

このSDカードリーダーは、SDカードアダプタを使わなくてもMicro SDカードを直接読み書きできるので便利です。

LANケーブルは、必須ではありませんが、HelioのLinuxイメージにデフォルトでセットアップされているWebサーバとsshdサーバ試したいので用意することにしました。

Win32DiskImagerのインストール

MicroSDブートディスクを書き込むために必要になるのでインストールしておきます。 こちらからダウンロードしました。

Tera Termのインストール

シリアル接続するためにTera Termが必要になるのでインストールしておきます。

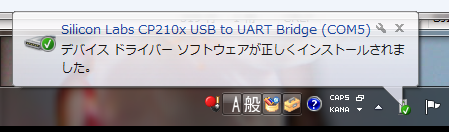

USB⇔シリアル接続のためのデバイスドライバのインストール

こちらからダウンロードしました。 64ビット環境なので、展開したzipファイルに含まれるCP210xVCPInstaller_x64.exeを実行します。

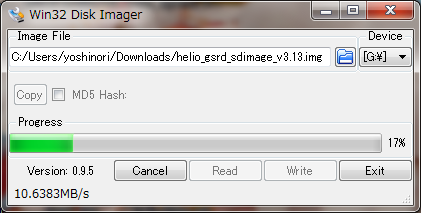

MicroSDブートディスクの作成

Getting Startedの「3. Creating a MicroSD boot disk from pre-built ALL in One Image」参考にMicroSDブートディスクを作成します。

Macnica Helio SoC Evaluation Kitからリンクされているhelio_gsrd_sdimage_v3.13.tar.gzが最新のようなので、こちらを使用します。

アーカイブを展開してイメージファイルを抽出します(cygwinを使いました)。2GBと結構大きいです。

$ tar zxvf helio_gsrd_sdimage_v3.13.tar.gz helio_gsrd_sdimage_v3.13.img $ ls -lh helio_gsrd_sdimage_v3.13.img -rw-r--r--+ 1 yoshinori None 2.0G 9月 4 16:27 helio_gsrd_sdimage_v3.13.img

Win32DiskImagerを起動して、イメージファイルを書き込みます。

各種接続の準備

HelioボードのPowerスイッチがOFFになっていることを確認して以下の通り機材を準備します。

DCジャックに電源ケーブルを接続します。

SDカードを挿入します。

LANケーブルを接続します。DHCPからIPアドレスをアサインしてもらうため、WiFiルーターのLANポートと接続しました。

USBケーブルは、J9 (UART)に接続します。ここでPCがデバイスを認識します。

Tera Termを起動し、COM5のBaud Rateを115200にして接続します。

Linuxのブート

HelioボードのPowerスイッチをONにするとTera TermにLinuxのブートシーケンスが表示された後にログイン受付状態になります。

Poky 8.0 (Yocto Project 1.3 Reference Distro) 1.3 socfpga ttyS0 socfpga login:

IPアドレスがDHCPからアサインされているのを確認しました。

root@socfpga:~# ifconfig

eth0 Link encap:Ethernet HWaddr a2:83:a1:16:02:17

inet addr:192.168.11.7 Bcast:0.0.0.0 Mask:255.255.255.0

UP BROADCAST RUNNING MULTICAST MTU:1500 Metric:1

RX packets:3 errors:0 dropped:0 overruns:0 frame:0

TX packets:6 errors:0 dropped:0 overruns:0 carrier:0

collisions:0 txqueuelen:1000

RX bytes:1240 (1.2 KiB) TX bytes:1248 (1.2 KiB)

Interrupt:152

lo Link encap:Local Loopback

inet addr:127.0.0.1 Mask:255.0.0.0

inet6 addr: ::1/128 Scope:Host

UP LOOPBACK RUNNING MTU:65536 Metric:1

RX packets:0 errors:0 dropped:0 overruns:0 frame:0

TX packets:0 errors:0 dropped:0 overruns:0 carrier:0

collisions:0 txqueuelen:0

RX bytes:0 (0.0 B) TX bytes:0 (0.0 B)

PCのブラウザから「http://192.168.11.7」(もちろん環境に依存します)にアクセスするとデモページが表示されました。

また、sshdが動いているので、Helioにsshで接続できることを確認しました。

おわりに

実はHelioボード上のWebデモページにLEDの制御のデモがあります。 これはWebアプリ(CGI)からFPGA側のLEDを制御するというもので、大変興味深いです。 しかし、残念ながら、今回の手順だけでは動きません。 Golden Hardware Reference Design (GHRD)をFPGAに予め書き込んでおく必要があります。 詳しくは次回紹介したいと思います。

HelioボードでFPGAによるLチカ

はじめに

FPGAに入門するため、Macnica Helio SoC評価ボードを購入しました。 今回はHelioボード内蔵のプッシュボタンとLEDを用いてブッシュボタンのON/OFFに応じてLEDを点灯してみます。

完成すると以下のような動作になります。

HelioボードでFPGA入門する人向けのまとまった良い情報が無かったので、詳しく記録に残しました。これからHelioボードでFPGAに入門する方などの参考になれば幸いです。

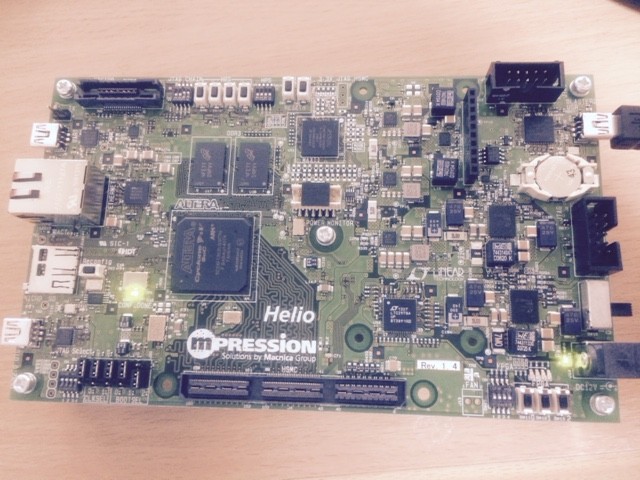

購入したHelioボード

Macnicaオンラインストアで購入しました。 税込みで28,000円ほどでした。 ACアダプターとUSBケーブル、8GB Micro SDカード、SDカードアダプタが付属しています。

準備

ボードのリビジョン確認

まず、ボードのリビジョンを確認します。Helioボードはこれまでに何回かリビジョン更新されているようです。ボードにシールが貼ってあり、それを見るとRev.1.4と書かれていました。この記事を書いている時点ではRev. 1.4が最新のようです。Rev 1.4の情報は、Helio Resources for Rev.1.4にまとまっています。

ボードレイアウト確認

Getting Startedでボードレイアウトを把握します。

良く見るとUSBポートが2つあります。Getting Startedの「2.2 External Connection」よると、用途は、

とのことです。

今回は、FPGAプログラミングをしたいので、後者のJ11のUSBポートに付属USBケーブルでPCを接続します。

その他ジャンパやDIPスイッチは、デフォルトのままにしておきます。

今回は、とりあえずFPGAのプログラミングが試せれば良いので、Getting Startedに記載されている以下のステップは省略します。

- Creating MicroSD boot disk for Helio Board

- Running Linux on Helio Board

ソフトウェアのセットアップ

Quartus II 14.1 Web Editionをセットアップします。Devicesには、Helioボードに搭載されているCyclone Vだけ動作すれば良いので「Cyclone V device support」以外のチェックは外します。 セットアップの終盤でAltera USB-Blaster IIをインストールするか聞かれるのでインストールしておきます。

作るもの

ボード内蔵のプッシュボタン2個とLED2個を使います。 プッシュボタンをA、Bとし、LEDをX、Yとすると、A and Bの時Xが点灯、A or Bの時、Yが点灯、となるようなものを作ります。

実装

ここから実装作業に入ります。

プロジェクトの作成

- Quartus IIを起動します。

- File -> New Project Wizard を選択します。

- Nextを選択します。

- 以下を入力して、Nextを選択します。

- Directory: C:/work/sample

- Name: SAMPLE

- Top-Level Entity: SAMPLE

- Empty projectのままNextを選択します。

- Add FilesはそのままNextを選択します。

- Family & Device SettingsはName FilterにFPGAチップの型番「5CSXFC5C6U23C7」を入力してNextを選択します。

- EDA Tool SettingsはそのままNextを選択します。

- 内容を確認して、問題なければFinishを選択します。

コーディング

FPGA関連の書籍ではじめて買ったはじめてのFPGA設計がVHDLで記述されていたので、VHDLを使います。

C:/work/sample/以下に空ファイルのsample.vhdを作成します。 Project NavigatorからFilesタブを選択し、Filesを右クリック->Add/Remove Files in Projectを選択します。 sample.vhdを選択して、追加します。

以下のコードを入力します。はじめてのFPGA設計のP29のリスト4-1のコードを使いました。

library ieee; use ieee.std_logic_1164.all; entity SAMPLE is port( A, B: in std_logic; X, Y: out std_logic ); end SAMPLE; architecture RTL of SAMPLE is begin X <= A and B; Y <= A or B; end RTL;

コンパイル

Processing -> Start Compileを選択します。 処理が完了するまでしばらくかかります。 Intel Core i7 870 @ 3GHzで3分弱かかりました。

導入したQuartus IIがWeb Editionのためか、以下の警告が表示されます。

「Warning (20028): Parallel compilation is not licensed and has been disabled」

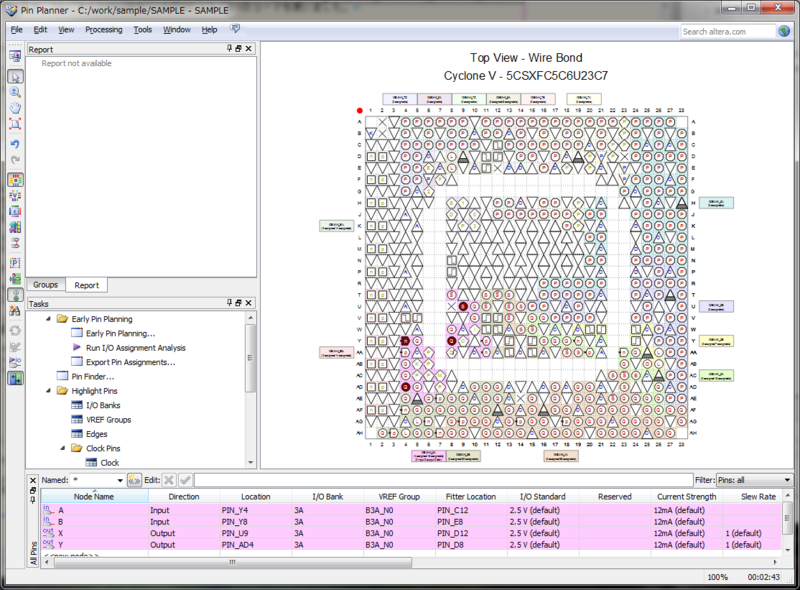

ピンの割り付け

コンパイルが完了すると、ピンの割り付けができるようになります。 sample.vhdに記述した、A、B、X、YにFPGAのピンに割り当てる作業になります。

ここでReference Manualを確認します。

「4.7.1 User-Defined push button」と「4.7.3 User-Defined LEDs」に、プッシュボタンとPin番号の情報が載っています。

- SW11 -> Y4

- SW12 -> Y8

- LED3 -> U9

- LED4 -> AD4

SW11をA、SW12をB、LED3をX、LED4をYと対応づけることにします。

ちなみに回路図が気になるなら、Schematicを確認します。Reference Manualに記載された仕様の通り結線されていることがわかります。

Assignments -> Pin Plannerを選択します。

AをY4にドラッグ&ドロップします。すると、AのLocationがPIN_Y4に設定されます。 残りも同様の作業を繰り返します。

すべての割り付け作業が完了すると、以下のようになります。

未使用のピンの処理

はじめてのFPGA設計によると、未使用のピンを処理しておかなないと、思わぬ誤動作やデバイスを破壊する恐れがあるとのことなので、設定しておきます。

- Assignments -> Deviceを選択します。

- Name FilterにFPGAチップの型番「5CSXFC5C6U23C7」を入力します。

- Device and Pin Optionsを選択します。

- Unused Pinsを選択します。

- As input tri-statedを選択します。

- OKを選択します。

フィッティング

Processing -> Start Compileを選択します。コンパイルの手順と同じですが、今回はピンの割り付けも加味されます。ここでも前回同様に3分弱かかりました。

FPGAに書き込む

手順を以下に示します。試行錯誤で見つけた手順なので変なやり方をしてるかもしれません。

- USBケーブルとDCケーブルを接続します。Power SwitchをONにします。PCがHelioを認識します。

- Tools -> Programmerを選択します。

- Hardware Setupを選択します。(3~5は1度だけでOK)

- Currently selected hardwareに「Helio [USB-1]」を選択します。

- Closeを選択します。

- Auto Detectを選択します。

- 「5CSXFC5C6」を選択します。

- 「5CSXFC5C6」を選択し、Deleteキーを入力します。SOCVHPSだけが残った状態にします。

- Add Fileを選択します。C:/work/sample/output_file/SAMPLE.sofを選択します。

- Startを選択します。

- 正常に書き込まれたら、Progressが100%になります。

参考に設定画面のキャプチャを載せます。

動作確認

期待する動作になることを確認します。ボードの電源を落とすとFPGAに書き込んだプログラムは消えます。

おわりに

FPGAをさわるのは今回がはじめてですが、なんとかLチカできました。