Helioボード同梱のLED制御Webアプリを動かす

はじめに

前回は、HelioボードでLinuxをブートできるようにしました。 今回は、Helio SDイメージに同梱されている、LED制御Webアプリを動作させます。LED制御デモを動作させるのにGolden Hardware Reference Design (GHRD)が必要になるのですが、その理由を明らかにします。 Qsysを用いてGHRDでARMプロセッサとオンボードのLEDがどのようにインターコネクトされているのかも確認します。

Golden Hardware Reference Design (GHRD)の入手

Helio Resources for Rev.1.4にあるhelio_ghrd_5csxc5_v14.0.zipをダウンロードし、展開します。

FPGAへのGHRDの書き込み

GHRDのoutput_filesディレクトリにはhelio_ghrd_top.sofがすでにあります。 ですので、ビルド工程をスキップしてFPGAにhelio_ghrd_top.sofを書き込みできます。 今回は同梱のSOFファイルを用いてFPGAに書き込んでみます。(時間短縮の意味でも楽です)

HelioをONにしてオンボードUSB Blaster IIにUSBケーブルを接続した状態で以下の手順を実施します。

- Quartus IIを起動します。

- File -> Open Projectを選択します。

- 展開したzipファイルのトップディレクトリにある「helio_ghrd_top.qpf」を選択します。

- Tools -> Programmerを選択します。

- Hardware SetupでHelioを選択します。

- Auto Detectを選択します。 7.「5CSXFC5C6」を選択します。

- 「5CSXFC5C6」を選択し、Deleteキーを入力します。SOCVHPSだけが残った状態にします。

- Add Fileを選択します。helio_ghrd_5csxc5_v14.0/output_files/helio_ghrd_top.sofを選択します。

- Startを選択します。

- 正常に書き込まれたら、Progressが100%になります。

成功すると、LEDがウエーブのように点灯します。

Linuxの起動

Helioの電源を入れた状態で以下の手順を実施します。

- USBケーブルをUARTに接続しなおします。

- LANケーブルを接続します。

- Tera Termでシリアル接続します。

- Warm Resetボタン(SW6)を押します。HPSにリセットがかかってLinuxが起動します。

LED制御デモ

ブラウザからHelioのIPアドレスにアクセスします。 アクセスしたページにLED制御デモがあるので試してみます。 LEDのウエーブの速さを変更したり、特定のLEDを点灯/消灯したりできます。

Webアプリと言ってもシンプルで、シェルスクリプトベースのCGIで組まれていて、LED制御プログラムをCGIから叩く仕組みになっているようです。

root@socfpga:/www/pages/cgi-bin# ls blink index.sh scroll_client scroll_server toggle

ちなみに、このディレクトリにある「blink」バイナリに対してstringsをかけてみると、「/sys/class/leds/fpga_led%d/」のような文字列が見つかります。 これから推測すると、おそらく、LEDを制御するデバイスドライバが別にあって、Sysfs経由でLED制御できるようにしてあるのだと思います。

root@socfpga:/www/pages/cgi-bin# strings blink

/lib/ld-linux-armhf.so.3

libpthread.so.0

_Jv_RegisterClasses

__gmon_start__

libc.so.6

sprintf

fopen

abort

fgets

fputs

fclose

fwrite

atoi

strcmp

__libc_start_main

GLIBC_2.4

xg{o

x`9`

x`9`H

?0F9FBF

/sys/class/leds/fpga_led%d/trigger

Failed to open the file %s

/sys/class/leds/fpga_led%d/brightness

none

--help

Usage %s: <LED number> <Blink delay (in ms)>

Invalid LED number. Valid LED range is 0-3

Invalid blink delay.

/home/root/.altera/frequency_fifo_scroll

Failed opening fifo frequency_fifo_scroll

/home/root/.altera/get_scroll_fifo

Failed opening fifo get_scroll_fifo

LED is scrolling.

Disable scroll_client before changing blink delay

/sys/class/leds/fpga_led%d/delay_on

/sys/class/leds/fpga_led%d/delay_off

timer

なぜGolden Hardware Reference Design (GHRD)が必要なのか?

GHRDにはHelioボードのHPS、LEDやボタンなどのサブシステム間のインターコネクトに関する情報などが入っていて、これをFPGAに書き込むことで、配線情報に従って結線されます。 つまり、LED制御デモが動かなかった原因は、GHRDをFPGAに書き込まないと、何も結線されていないので、ARMプロセッサからLEDが見えないため、ということになります。

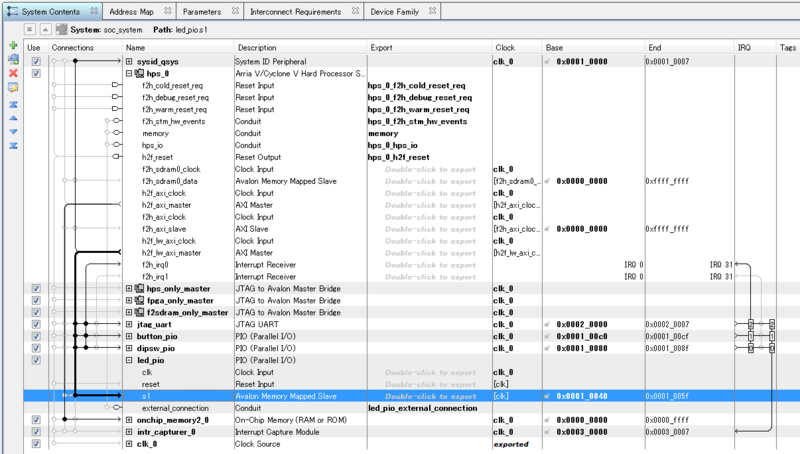

Qsysによるインターコネクトの確認

GHRDのインターコネクトはQsysで確認できます。

- Qsysを起動します。

- helio_ghrd_5csxc5_v14.0/soc_system.qsysを選択します。

hps_0は、ARMプロセッサのインタフェースです。 led_pioは、LED制御用のパラレルインタフェースです。 hps_0のh2f_lw_axi_master(※)とled_pioのs1が結線されていることがわかります。これは、つまり、ARMプロセッサからMemory-mapped I/Oでパラレル接続されているLEDを制御する、ということを意味しています。

※h2fとはHPS to FPGAのことで、信号の方向を表現しています。

led_pioはPIOコアと呼ばれるIPコアを用いています。詳細仕様は、led_pioをダブルクリックして、Detailsボタンを選択するとデータシートへのリンクがあるので、そちらを参照します。

led_pioのパラメータを確認すると、Widthが4になっているので、4bitのパラレルインタフェースであることがわかります。制御対象のオンボードLEDの個数と一致しています。

おわりに

LEDをCGIから制御するデモが動きました。 QsysでGolden Hardware Reference Desigのインターコネクトを確認することで、Helioボード同梱のLED制御デモでは、ARMプロセッサからMemory-mapped I/OでLEDを制御していることがわかりました。今回の経験から、ARMプロセッサとFPGAの世界をつなぐ手法としてMemory-mapped I/Oの理解がポイントになりそうです。